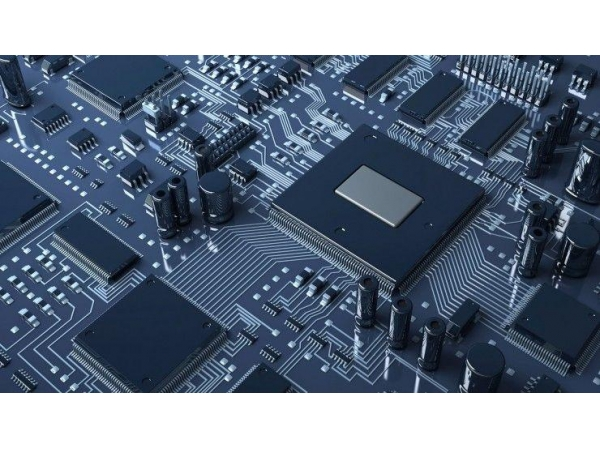

ယနေ့ခေတ် MOS ဒရိုက်ဘာများနှင့်အတူ၊ ထူးကဲသောလိုအပ်ချက်များစွာရှိသည်။

1. အနိမ့်ဗို့အားလျှောက်လွှာ

5V ၏လျှောက်လွှာကိုပြောင်းသောအခါလျှပ်စစ်ဓာတ်အားထုတ်ပေးသောကိရိယာရိုးရာ totem တိုင်ဖွဲ့စည်းပုံကိုအသုံးပြုပါက၊ triode သည် 0.7V သာရှိပြီး အတက်အဆင်းဆုံးရှုံးမှုရှိသောကြောင့် ဗို့အားမှာ 4.3V သာရှိသောကြောင့် နောက်ဆုံးအဆင့်တွင် gate ၏သတ်မှတ်ထားသောနောက်ဆုံးဝန်ကိုရရှိစေသောကြောင့်၊ ယခုအချိန်တွင် ခွင့်ပြုထားသောဂိတ်ဗို့အားအသုံးပြုခြင်း၊ 4.5V ၏MOSFETs အန္တရာယ် အတိုင်းအတာ အတိုင်းအတာတစ်ခုအထိ ရှိပါတယ်။အခြေအနေ အတူတူပါပဲ။ 3V သို့မဟုတ် အခြားသော ဗို့အားနိမ့်ပြောင်းပါဝါထောက်ပံ့မှု၏ အသုံးချမှုတွင်လည်း ဖြစ်ပေါ်သည်။

2.Wide ဗို့အားလျှောက်လွှာ

သော့ချိတ်ဗို့အားတွင် ကိန်းဂဏာန်းတန်ဖိုးမရှိပါ၊ ၎င်းသည် အခါအားလျော်စွာ သို့မဟုတ် အခြားအချက်များကြောင့် ကွဲပြားသည်။ ဤပြောင်းလဲမှုသည် PWM ဆားကစ်မှ MOSFET သို့ပေးသော drive ဗို့အား မတည်မငြိမ်ဖြစ်စေသည်။

မြင့်မားသောဂိတ်ဗို့အားများတွင် MOSFET ကို ပိုမိုကောင်းမွန်စွာ လုံခြုံစေရန်အတွက်၊ MOSFET အများအပြားသည် ဂိတ်ဗို့အား၏ပြင်းအားကို ကန့်သတ်ရန် အတင်းအကြပ်ပြုလုပ်ရန် ဗို့အားထိန်းညှိကိရိယာများကို ထည့်သွင်းထားသည်။ ဤကိစ္စတွင်၊ drive voltage ကို regulator ၏ဗို့အား ကျော်လွန်သွားသောအခါ၊ static function ဆုံးရှုံးမှုကြီး ဖြစ်ပေါ်လာသည်။

တစ်ချိန်တည်းမှာပင်၊ အကယ်၍ resistor voltage divider ၏အခြေခံနိယာမကိုအသုံးပြုပါက၊ သော့ဗို့အားပိုမိုမြင့်မားပါက MOSFET သည်ကောင်းမွန်စွာအလုပ်လုပ်ပြီး၊ သော့ဗို့အားလျော့သွားပါက၊ gate voltage သည်မဖြစ်နိုင်ပါ။ လုံလောက်သော၊ လုံလောက်သောအဖွင့်နှင့်အဖွင့်အပိတ်သည်မလုံလောက်ဘဲ၊ လုပ်ဆောင်မှုဆုံးရှုံးမှုကိုတိုးမြင့်စေသည်။

3. Dual ဗို့အားအသုံးချမှု

ထိန်းချုပ်ဆားကစ်အချို့တွင်၊ ဆားကစ်၏ လော့ဂျစ်အပိုင်းသည် ပုံမှန် 5V သို့မဟုတ် 3.3V ဒေတာဗို့အားကို သက်ရောက်စေပြီး အထွက်ပါဝါအပိုင်းသည် 12V သို့မဟုတ် ထို့ထက်ပို၍ သက်ရောက်ပြီး ဗို့အားနှစ်ခုကို ဘုံမြေနှင့် ချိတ်ဆက်ထားသည်။

၎င်းသည် ပါဝါထောက်ပံ့ရေးပတ်လမ်းကို အသုံးပြုရမည်ဖြစ်ပြီး ဗို့အားနိမ့်ဘက်ခြမ်းသည် မြင့်မားသောဗို့အား MOSFET ကို ကျိုးကြောင်းဆီလျော်စွာ ကိုင်တွယ်နိုင်စေရန်အတွက် ဗို့အားမြင့် MOSFET သည် 1 နှင့် 2 တွင်ဖော်ပြထားသော အလားတူအခက်အခဲများကို ရင်ဆိုင်ဖြေရှင်းနိုင်မည်ဖြစ်ကြောင်း ရှင်းလင်းစေသည်။

ဤသုံးမျိုးတွင်၊ totem တိုင်တည်ဆောက်မှုသည် output လိုအပ်ချက်များနှင့်မကိုက်ညီပါ၊ နှင့် ရှိပြီးသား MOS ဒရိုက်ဘာ IC အများအပြားတွင် gate voltage limiting construction မပါဝင်ပါ။