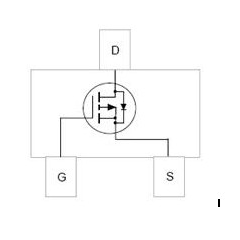

ပထမဦးစွာ၊ MOSFET အမျိုးအစားနှင့်ဖွဲ့စည်းပုံ၊ MOSFET သည် FET (နောက်တစ်မျိုးမှာ JFET) ဖြစ်ပြီး၊ P-channel သို့မဟုတ် N-channel အမျိုးအစား စုစုပေါင်း လေးမျိုးဖြင့် ထုတ်လုပ်နိုင်သော်လည်း ပိုမိုကောင်းမွန်သော N ကိုသာ အသုံးပြုနိုင်မည်ဖြစ်သည်။ -channel MOSFETs နှင့် အဆင့်မြှင့်ထားသော P-channel MOSFETs၊ ထို့ကြောင့် အများအားဖြင့် NMOSFET ဟုရည်ညွှန်းသည်၊ သို့မဟုတ် PMOSFET သည် များသောအားဖြင့် ဖော်ပြထားသော NMOSFET သို့မဟုတ် PMOSFET ကိုရည်ညွှန်းသည် ဤနှစ်မျိုးကိုရည်ညွှန်းသည်။ ဤအဆင့်မြှင့်တင်ထားသော MOSFET အမျိုးအစားနှစ်မျိုးအတွက်၊ ၎င်းတို့၏ ခံနိုင်ရည်နည်းပါးပြီး ထုတ်လုပ်ရလွယ်ကူသောကြောင့် NMOSFET များကို ပို၍အသုံးများပါသည်။ ထို့ကြောင့် NMOSFET များကို power supply နှင့် motor drive applications များပြောင်းရာတွင် ယေဘူယျအားဖြင့် အသုံးပြုကြပြီး အောက်ဖော်ပြပါ နိဒါန်းတွင် NMOSFETs များကို အလေးထားပါသည်။ parasitic capacitance သည် pin သုံးခုကြားတွင်တည်ရှိသည်။MOSFETမလိုအပ်သော်လည်း ထုတ်လုပ်မှုလုပ်ငန်းစဉ်၏ ကန့်သတ်ချက်များကြောင့်ဖြစ်သည်။ parasitic capacitance သည် driver circuit တစ်ခုကို ဒီဇိုင်းဆွဲရန် သို့မဟုတ် ရွေးချယ်ရန် အနည်းငယ် ခက်ခဲစေသည်။ မြောင်းနှင့် အရင်းအမြစ်ကြားတွင် ကပ်ပါးဒိုင်အိုဒတစ်ခုရှိသည်။ ၎င်းကို body diode ဟုခေါ်ပြီး မော်တာကဲ့သို့သော inductive load များကို မောင်းနှင်ရာတွင် အရေးကြီးပါသည်။ စကားမစပ်၊ body diode သည် MOSFETs တစ်ခုစီတွင်သာရှိပြီး များသောအားဖြင့် IC ချစ်ပ်တစ်ခုအတွင်း၌ မရှိပေ။

ယခုMOSFET5V ပါဝါထောက်ပံ့မှုကိုအသုံးပြုသောအခါ၊ ဗို့အားနိမ့်အက်ပလီကေးရှင်းများကိုမောင်းနှင်ပါ၊ ဤတစ်ကြိမ်တွင်သင်ရိုးရိုး totem တိုင်ဖွဲ့စည်းပုံကိုအသုံးပြုပါက၊ ထရန်စစ္စတာသည် 0.7V ဗို့အားကျဆင်းသွားခြင်းကြောင့် အမှန်တကယ်နောက်ဆုံးပေါ်ရှိ gate တွင်ထည့်ထားသောဗို့အားသည်သာဖြစ်သည်။ 4.3 V. ဤအချိန်တွင်၊ ကျွန်ုပ်တို့သည် အချို့သောအန္တရာယ်များရှိကြောင်းအတွက် MOSFET ၏အမည်ခံတံခါးဗို့အား 4.5V ကိုရွေးချယ်ပါသည်။ 3V သို့မဟုတ် အခြားဗို့အားနည်းပါးသော ပါဝါထောက်ပံ့မှုအချိန်များတွင် တူညီသောပြဿနာ ဖြစ်ပေါ်ပါသည်။ လော့ဂျစ်အပိုင်းသည် ပုံမှန် 5V သို့မဟုတ် 3.3V ဒစ်ဂျစ်တယ်ဗို့အားကို အသုံးပြုပြီး ပါဝါအပိုင်းသည် 12V သို့မဟုတ် ထို့ထက်ပို၍ အသုံးပြုသည့် ထိန်းချုပ် circuit အချို့တွင် Dual ဗို့အားကို အသုံးပြုပါသည်။ ဗို့အားနှစ်ခုသည် ဘုံမြေကို အသုံးပြု၍ ချိတ်ဆက်ထားသည်။ ၎င်းသည် ဗို့အားမြင့်ဘက်ခြမ်းရှိ MOSFET အား ဗို့အားနိမ့်ဘက်ခြမ်းအား ထိရောက်စွာ ထိန်းချုပ်နိုင်စေမည့် ဆားကစ်တစ်ခုကို အသုံးပြုရန် လိုအပ်ပြီး ဗို့အားမြင့်ဘေးရှိ MOSFET သည် 1 နှင့် 2 တွင်ဖော်ပြထားသော အလားတူပြဿနာများကို ရင်ဆိုင်ရမည်ဖြစ်သည်။

ကိစ္စသုံးမျိုးလုံးတွင်၊ Totem တိုင်တည်ဆောက်ပုံသည် အထွက်လိုအပ်ချက်များကို မဖြည့်ဆည်းနိုင်ဘဲ၊ စင်ပြင်ပရှိ MOSFET ဒရိုက်ဘာ IC အများအပြားတွင် ဂိတ်ဗို့အားကန့်သတ်ဖွဲ့စည်းပုံ မပါဝင်ပါ။ အဝင်ဗို့အားသည် ပုံသေတန်ဖိုးမဟုတ်ပါ၊ ၎င်းသည် အချိန် သို့မဟုတ် အခြားအချက်များနှင့် ကွဲပြားသည်။ ဤပြောင်းလဲမှုသည် PWM ဆားကစ်မှ MOSFET သို့ပေးသော drive ဗို့အား မတည်မငြိမ်ဖြစ်စေသည်။ MOSFET ကို high gate voltages များမှ ဘေးကင်းစေရန်အတွက်၊ MOSFET အများအပြားတွင် gate voltage ၏ amplitude ကို အတင်းအကျပ်ကန့်သတ်ရန် built-in voltage regulator ရှိသည်။ ဤကိစ္စတွင်၊ drive voltage သည် voltage regulator ထက်ပိုမိုပေးသောအခါ၊ ၎င်းသည် တစ်ချိန်တည်းတွင် static power သုံးစွဲမှုကြီးမားလိမ့်မည်၊ အကယ်၍ သင်သည် gate voltage ကိုလျှော့ချရန် resistor voltage divider ၏နိယာမကိုရိုးရှင်းစွာအသုံးပြုပါက၊ gate voltage ကိုလျှော့ချရန်အတော်လေးမြင့်မားလိမ့်မည်၊ input voltage, theMOSFETဂိတ်ဗို့အား ပြီးပြည့်စုံသော conduction ထက်နည်းစေရန် မလုံလောက်သောအခါ input ဗို့အား လျော့သွားချိန်တွင် ကောင်းစွာအလုပ်လုပ်သည်၊ ထို့ကြောင့် ပါဝါသုံးစွဲမှုကို တိုးစေသည်။

ရိုးရှင်းသောခွဲခြမ်းစိတ်ဖြာမှုပြုလုပ်ရန် NMOSFET ဒရိုင်ဘာဆားကစ်အတွက်သာ ဤနေရာတွင်အတော်လေးဘုံဘုံပတ်လမ်းဖြစ်သည်- Vl နှင့် Vh တို့သည် low-end နှင့် high-end power supply ဖြစ်သည်၊ ဗို့အားနှစ်ခုသည်တူညီနိုင်သော်လည်း Vl သည် Vh ထက်မပိုသင့်ပါ။ Q1 နှင့် Q2 သည် အထီးကျန်မှုကို နားလည်ရန် အသုံးပြုပြီး တစ်ချိန်တည်းတွင် ဒရိုင်ဘာပြွန် Q3 နှင့် Q4 နှစ်ခုသည် တစ်ချိန်တည်းတွင် စီးဆင်းမှုမဟုတ်ကြောင်း သေချာစေရန်အတွက် Q1 နှင့် Q2 သည် ပြောင်းပြန် totem တိုင်တစ်ခုဖြစ်သည်။ R2 နှင့် R3 သည် PWM ဗို့အား R2 နှင့် R3 သည် PWM ဗို့အားရည်ညွှန်းချက်ကို ပံ့ပိုးပေးသည်၊ ဤအကိုးအကားကို ပြောင်းလဲခြင်းဖြင့်၊ သင်သည် PWM အချက်ပြလှိုင်းပုံစံတွင် ဆားကစ်ကို မတ်စောက်ပြီး ဖြောင့်တန်းသော အနေအထားတွင် လုပ်ဆောင်နိုင်သည်။ Q3 နှင့် Q4 ကို အချိန်မှန်၊ Q3 နှင့် Q4 သည် Vh နှင့် GND နှင့် ဆက်စပ်နေသောကြောင့် Vce ဗို့အားကျဆင်းမှု အနည်းဆုံးဖြစ်ပြီး၊ ဤဗို့အားကျဆင်းမှုသည် အများအားဖြင့် 0.3V သို့မဟုတ် ထို့ထက် ပိုနည်းသောကြောင့်၊ 0.7V Vce R5 နှင့် R6 ထက် တုံ့ပြန်မှု ခံနိုင်ရည်များ ဖြစ်သည်၊ ဂိတ် R5 နှင့် R6 အတွက် အသုံးပြုသည့် တုံ့ပြန်မှု ခုခံမှု များသည် ဂိတ်ဗို့အား နမူနာယူရန် အသုံးပြုသည့် တုံ့ပြန်မှု ခုခံမှု ပစ္စည်းများ ဖြစ်ပြီး၊ ထို့နောက် အောက်ခံများအပေါ် ခိုင်ခံ့သော အနုတ်လက္ခဏာ တုံ့ပြန်ချက် ထုတ်ပေးရန်အတွက် Q5 မှတဆင့် ဖြတ်သွားပါသည်။ Q1 နှင့် Q2 ၏ gate voltage ကို အကန့်အသတ်တန်ဖိုးအဖြစ် ကန့်သတ်ထားသည်။ ဤတန်ဖိုးကို R5 နှင့် R6 ဖြင့်ချိန်ညှိနိုင်သည်။ နောက်ဆုံးတွင်၊ R1 သည် Q3 နှင့် Q4 သို့အခြေခံလျှပ်စီးကြောင်းကန့်သတ်ချက်ကိုပေးသည်၊ R4 သည် Q3Q4 ၏ရေခဲ၏ကန့်သတ်ချက်ဖြစ်သည့် MOSFETs အတွက်တံခါးပေါက်လက်ရှိကန့်သတ်ချက်ကိုပေးသည်။ လိုအပ်ပါက Acceleration Capacitor ကို R4 အထက်တွင် အပြိုင်ချိတ်ဆက်နိုင်သည်။