MOSFET တွေရဲ့ အခန်းကဏ္ဍက ဘာလဲ။

MOSFET များသည် ပါဝါထောက်ပံ့မှုစနစ်တစ်ခုလုံး၏ ဗို့အားကိုထိန်းညှိရာတွင် အခန်းကဏ္ဍတစ်ခုမှ ပါဝင်ပါသည်။ လောလောဆယ်တွင်၊ ဘုတ်ပေါ်တွင်အသုံးပြုသော MOSFET အများအပြားမရှိပါ၊ ပုံမှန်အားဖြင့် 10 လုံးခန့်ရှိသည်။ အဓိကအကြောင်းရင်းမှာ MOSFET အများစုကို IC ချစ်ပ်သို့ပေါင်းစည်းထားခြင်းကြောင့်ဖြစ်သည်။ MOSFET ၏ အဓိကအခန်းကဏ္ဍမှာ ဆက်စပ်ပစ္စည်းများအတွက် တည်ငြိမ်သောဗို့အားကို ပေးဆောင်ရန်ဖြစ်သောကြောင့်၊ CPU၊ GPU နှင့် socket စသည်တို့တွင် ယေဘူယျအားဖြင့် အသုံးပြုပါသည်။MOSFETsယေဘုယျအားဖြင့် အပေါ်နှင့်အောက် နှစ်ခုအုပ်စုတစ်စု၏ပုံစံသည် ဘုတ်ပေါ်တွင်ပေါ်လာသည်။

MOSFET အထုပ်

ထုတ်လုပ်မှုတွင် MOSFET ချစ်ပ်ပြား ပြီးသွားသည်၊ ဆိုလိုသည်မှာ MOSFET ပက်ကေ့ဂျ်တွင် အခွံတစ်ခု ထည့်ရန် လိုအပ်သည်။ MOSFET ချစ်ပ်ခွံသည် ပံ့ပိုးမှု၊ ကာကွယ်မှု၊ အအေးပေးသည့်အကျိုးသက်ရောက်မှုရှိပြီး လျှပ်စစ်ချိတ်ဆက်မှုနှင့် အထီးကျန်မှုကို ပံ့ပိုးပေးသည့် ချစ်ပ်အတွက်၊ ထို့ကြောင့် MOSFET စက်နှင့် အခြားအစိတ်အပိုင်းများကို ပြီးပြည့်စုံသော ဆားကစ်တစ်ခုအဖြစ် ဖန်တီးနိုင်စေရန်။

PCB တွင် တပ်ဆင်နည်းနှင့်အညီ ခွဲခြားခြင်း၊MOSFETပက်ကေ့ဂျ်တွင် အဓိက အမျိုးအစား နှစ်မျိုး ရှိသည်- အပေါက်ဖောက်ခြင်းနှင့် Surface Mount။ PCB ပေါ်တွင် ဂဟေဆော်ထားသော PCB အပေါက်များမှတဆင့် MOSFET pin ကို ထည့်သွင်းထားသည်။ Surface Mount သည် MOSFET pin နှင့် heat sink flange ကို PCB မျက်နှာပြင် pads များနှင့် ချိတ်ဆက်ထားသည်။

Standard Package Specifications TO Package

TO (Transistor Out-line) သည် TO-92၊ TO-92L၊ TO-220၊ TO-252 ကဲ့သို့သော အစောပိုင်း package specification များသည် plug-in package design များဖြစ်သည်။ မကြာသေးမီနှစ်များအတွင်း၊ မျက်နှာပြင် mount စျေးကွက်ဝယ်လိုအား မြင့်တက်လာပြီး TO ပက်ကေ့ချ်များသည် မျက်နှာပြင် mount ပက်ကေ့ဂျ်များအထိ တိုးတက်လာသည်။

TO-252 နှင့် TO263 များသည် မျက်နှာပြင်တပ်ဆင်မှု ပက်ကေ့ခ်ျများဖြစ်သည်။ TO-252 ကို D-PAK လို့လည်း ခေါ်ကြပြီး TO-263 ကို D2PAK လို့လည်း ခေါ်ကြပါတယ်။

D-PAK အထုပ်တွင် MOSFET တွင် လျှပ်ကူးပစ္စည်း (Gate)၊ မြောင်း (D)၊ အရင်းအမြစ် (S) သုံးခုရှိသည်။ မြောင်း (D) pin များကို မြောင်း (D) အတွက် heat sink ၏ နောက်ကျောကို အသုံးမပြုဘဲ ဖြတ်တောက်ပြီး တစ်ဖက်မှ PCB သို့ တိုက်ရိုက် ဂဟေဆော်ကာ မြင့်မားသော လျှပ်စီးကြောင်း၏ အထွက်အတွက်၊ တစ်ဖက်တွင်၊ PCB အပူ dissipation ။ ထို့ကြောင့် PCB D-PAK pads သုံးခုရှိသည်၊ မြောင်း (D) pad သည်ပိုကြီးသည်။

အထုပ် TO-252 pin diagram

DIP (Dual ln-line Package ဟုရည်ညွှန်းသော DIP (Dual ln-line Package) ဟုရည်ညွှန်းသော လူကြိုက်များသော သို့မဟုတ် လိုင်းနှစ်လိုင်းပက်ကေ့ချ်။ DIP ပက်ကေ့ဂျ်တွင် ထိုအချိန်က သင့်လျော်သော PCB (ပုံနှိပ်ဆားကစ်ဘုတ်) ဖောက်ထွင်းတပ်ဆင်မှုရှိပြီး TO-type ပက်ကေ့ချ် PCB ဝိုင်ယာကြိုးများနှင့် လည်ပတ်မှုထက် ပိုမိုလွယ်ကူသည်။ ပိုမိုအဆင်ပြေပြီး အလွှာပေါင်းများစွာရှိသော Ceramic Dual in-line DIP၊ single-layer Ceramic Dual အပါအဝင် ပုံစံများစွာဖြင့် ၎င်း၏ အထုပ်ဖွဲ့စည်းပုံ၏ ဝိသေသလက္ခဏာအချို့အပေါ်၊ တန်းဝင်ကာစီသည်

DIP၊ ခဲဘောင် DIP စသည်ဖြင့်။ ပါဝါထရန်စစ္စတာများ၊ ဗို့အားထိန်းညှိခြင်း ချစ်ပ်အထုပ်များတွင် အသုံးများသည်။

ချစ်ပ်MOSFETအထုပ်

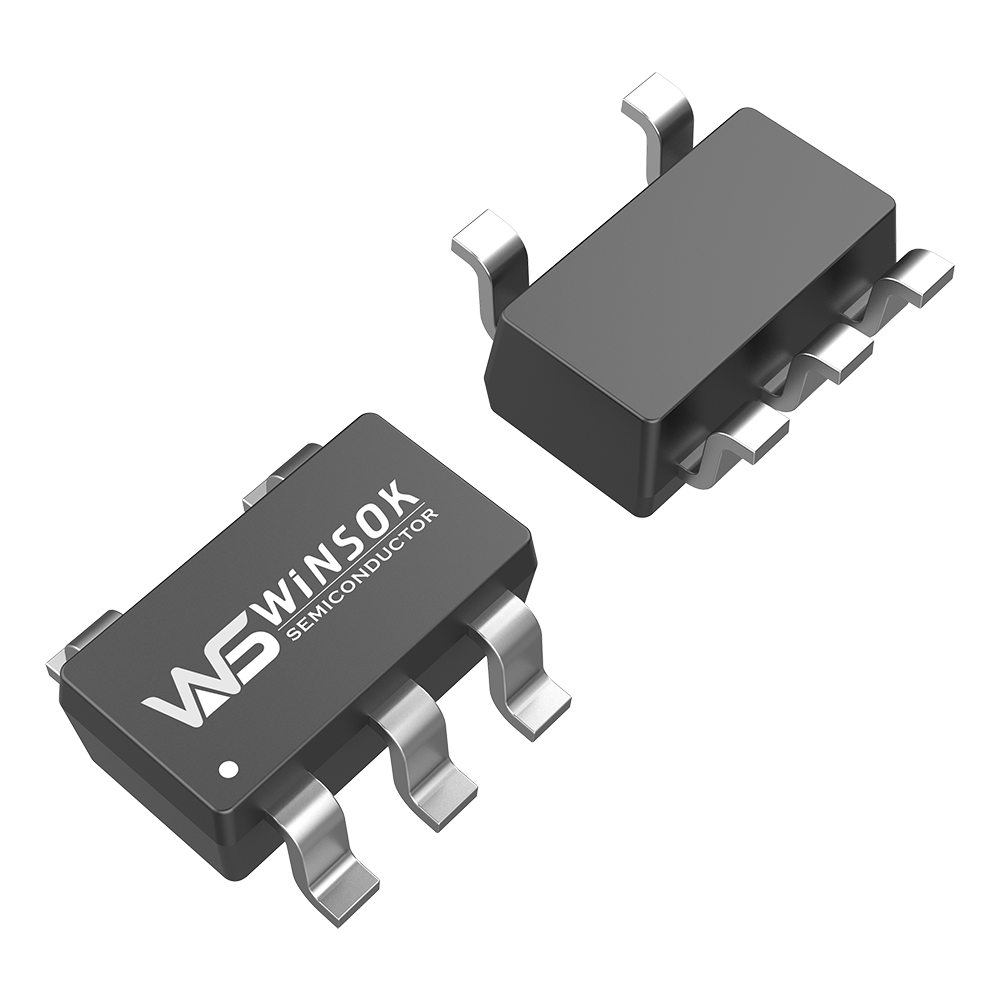

SOT Package

SOT (Small Out-Line Transistor) သည် သေးငယ်သော outline ထရန်စစ္စတာ အထုပ်တစ်ခုဖြစ်သည်။ ဤပက်ကေ့ချ်သည် ယေဘုယျအားဖြင့် သေးငယ်သော ပါဝါ MOSFET အတွက် အသုံးပြုသည့် TO ပက်ကေ့ထက် ပိုသေးငယ်သော SMD အသေးစား ပါဝါထရန်စစ္စတာ ပက်ကေ့ခ်ျတစ်ခုဖြစ်သည်။

SOP Package

SOP (Small Out-Line Package) သည် တရုတ်ဘာသာတွင် "သေးငယ်သော ကောက်ကြောင်း ပက်ကေ့ချ်" ဟု အဓိပ္ပါယ်ရပြီး SOP သည် မျက်နှာပြင် တပ်ဆင်သည့် ပက်ကေ့ခ်ျများထဲမှ တစ်ခုဖြစ်ပြီး စင်ရော်တောင်ပံပုံသဏ္ဍာန် (L-shaped) အထုပ်၏ ဘေးနှစ်ဖက်မှ တံများ၊ ပလတ်စတစ်နှင့် ကြွေထည်များဖြစ်သည်။ SOP ကို SOL နှင့် DFP ဟုခေါ်သည်။ SOP ပက်ကေ့ဂျ်စံနှုန်းများတွင် SOP-8၊ SOP-16၊ SOP-20၊ SOP-28 စသည်ဖြင့်၊ SOP ပြီးနောက် နံပါတ်သည် ပင်နံပါတ်များကို ညွှန်ပြပါသည်။

MOSFET ၏ SOP ပက်ကေ့ဂျ်သည် အများအားဖြင့် SOP-8 သတ်မှတ်ချက်ကို လက်ခံသည်၊ လုပ်ငန်းသည် SO (Small Out-Line) ဟုခေါ်သော "P" ကို ချန်လှပ်ထားတတ်သည်။

SMD MOSFET အထုပ်

SO-8 ပလပ်စတစ်အထုပ်၊ အပူအခြေခံပန်းကန်မရှိ၊ ညံ့ဖျင်းသောအပူပေးစနစ်၊ ယေဘုယျအားဖြင့် စွမ်းအားနည်း MOSFET အတွက် အသုံးပြုသည်။

SO-8 ကို PHILIP မှ စတင်တီထွင်ခဲ့ပြီး TSOP (ပါးလွှာသော ကောက်ကြောင်းအထုပ်ငယ်)၊ VSOP (အလွန်သေးငယ်သော ကောက်ကြောင်းအထုပ်)၊ SSOP (လျှော့ချထားသော SOP)၊ TSSOP (ပါးလွှာသော SOP) နှင့် အခြားသော စံသတ်မှတ်ချက်များမှ တဖြည်းဖြည်း ဆင်းသက်လာသည်။

ဤရရှိလာသော ပက်ကေ့ချ်သတ်မှတ်ချက်များအနက် TSOP နှင့် TSSOP ကို MOSFET ပက်ကေ့ဂျ်များအတွက် အသုံးများသည်။

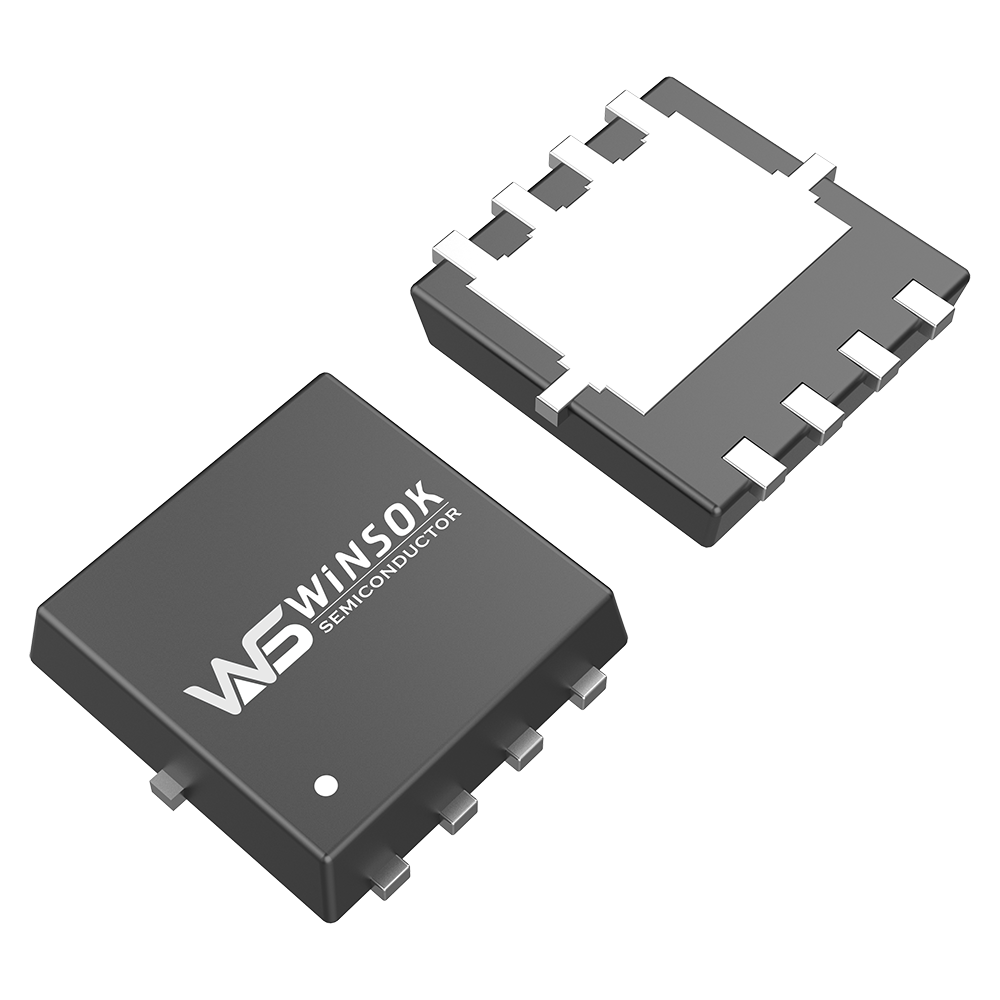

ချစ်ပ် MOSFET ပက်ကေ့ခ်ျများ

QFN (Quad Flat Non-leaded package) သည် မျက်နှာပြင် mount ပက်ကေ့ဂျ်များထဲမှ တစ်ခုဖြစ်ပြီး၊ လေးဘက်ခြမ်း ခဲမဟုတ်သော အပြားအထုပ်ဟု တရုတ်လူမျိုးများက ခေါ်ဝေါ်သော pad အရွယ်အစားသည် သေးငယ်သည်၊ သေးငယ်သည်၊ ပလပ်စတစ်သည် ပေါ်ထွက်လာသော မျက်နှာပြင်ချပ်စ်၏ အလုံပိတ်ပစ္စည်းအဖြစ်၊ ထုပ်ပိုးမှုနည်းပညာကို ယခုအခါ LCC ဟုခေါ်သည်။ ၎င်းကို ယခု LCC ဟုခေါ်ပြီး QFN သည် Japan Electrical and Mechanical Industries Association မှ သတ်မှတ်သော အမည်ဖြစ်ပါသည်။ ပက်ကေ့ဂျ်ကို နှစ်ဖက်စလုံးတွင် လျှပ်ကူးပစ္စည်း အဆက်အသွယ်များဖြင့် ပြင်ဆင်ထားသည်။

ပက်ကေ့ဂျ်ကို လေးဘက်စလုံးရှိ လျှပ်ကူးပစ္စည်းအဆက်အသွယ်များဖြင့် စီစဉ်သတ်မှတ်ထားပြီး ခဲများမရှိသောကြောင့်၊ တပ်ဆင်သည့်ဧရိယာသည် QFP ထက်သေးငယ်ပြီး အမြင့်သည် QFP ထက်နိမ့်သည်။ ဤပက်ကေ့ဂျ်ကို LCC၊ PCLC၊ P-LCC စသည်ဖြင့် လူသိများသည်။