အဓိက အကြောင်းအရင်း နှစ်ချက်of MOSFET ရှုံးနိမ့်မှု-

ဗို့အားချို့ယွင်းမှု- ဆိုလိုသည်မှာ၊ မြောင်းနှင့်ရင်းမြစ်ကြားရှိ BVdss ဗို့အားသည် စံသတ်မှတ်ထားသော ဗို့အားထက် ကျော်လွန်နေသည်။MOSFET နဲ့ ရောက်တယ်။ အချို့သောစွမ်းရည်ကြောင့် MOSFET ကိုပျက်ကွက်စေသည်။

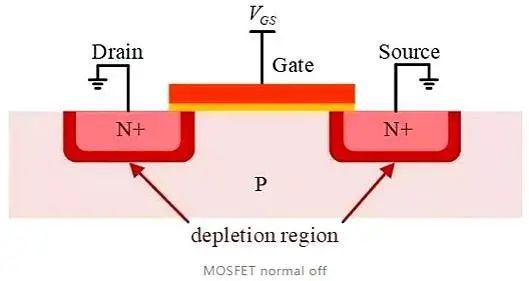

ဂိတ်ဗို့အား ချို့ယွင်းမှု- ဂိတ်သည် ပုံမှန်မဟုတ်သော ဗို့အားတက်နေသဖြင့် ဂိတ်ပေါက်အောက်ဆီဂျင် ချို့ယွင်းမှု ဖြစ်ပေါ်သည်။

ပြိုကျပြတ်ရွေ့ (ဗို့အားချို့ယွင်းမှု)

နှင်းပြိုကျမှု အတိအကျက ဘာလဲ။ ရိုးရိုးရှင်းရှင်းပြောရရင်၊MOSFET တစ်ခု ဘတ်စ်ဗို့အားများ၊ ထရန်စဖော်မာ ရောင်ပြန်ဟပ်မှု ဗို့အားများ၊ ယိုစိမ့်မှုဗို့အားများ စသည်တို့နှင့် MOSFET တို့အကြား superposition မှ ဖန်တီးထားသော ချို့ယွင်းမှုမုဒ်တစ်ခုဖြစ်သည်။ အတိုချုပ်အားဖြင့်၊ MOSFET ၏ မြောင်း-ရင်းမြစ်ဝင်ရိုးစွန်းမှ ဗို့အားသည် ၎င်း၏ သတ်မှတ်ထားသော ဗို့အားတန်ဖိုးထက် ကျော်လွန်ကာ စွမ်းအင်ကန့်သတ်ချက်တစ်ခုသို့ ရောက်ရှိသောအခါ ဖြစ်လေ့ရှိသော ချို့ယွင်းမှုတစ်ခုဖြစ်သည်။

နှင်းပြိုကျခြင်းများကို ကာကွယ်ရန် အစီအမံများ

- ဆေးပမာဏကို သင့်လျော်စွာ လျှော့ချပါ။ ဤလုပ်ငန်းတွင် အများအားဖြင့် 80-95% လျှော့ချသည်။ ကုမ္ပဏီ၏ အာမခံစည်းမျဉ်းများနှင့် လိုင်းဦးစားပေးများကို အခြေခံ၍ ရွေးချယ်ပါ။

- Reflective Voltage သည် သင့်လျော်သည်။

-RCD၊ TVS စုပ်ယူမှု circuit ဒီဇိုင်းသည် သင့်လျော်သည်။

- parasitic inductance နည်းပါးစေရန်အတွက် မြင့်မားသော ဝိုင်ယာကြိုးများသည် တတ်နိုင်သမျှ ကျယ်သင့်သည်။

- သင့်လျော်သော Gate resistor Rg ကိုရွေးချယ်ပါ။

- လိုအပ်သလို မြင့်မားသောပါဝါထောက်ပံ့မှုအတွက် RC damping သို့မဟုတ် Zener diode စုပ်ယူမှုကို ပေါင်းထည့်ပါ။

Gate Voltage Failure

ပုံမှန်မဟုတ်သောမြင့်မားသောဂရစ်ဗို့အားများဖြစ်စေသော အဓိကအကြောင်းရင်းသုံးမျိုးရှိသည်- ထုတ်လုပ်မှု၊ သယ်ယူပို့ဆောင်ရေးနှင့် တပ်ဆင်စဉ်အတွင်း တည်ငြိမ်လျှပ်စစ်ဓာတ်အား၊ ပါဝါစနစ်လည်ပတ်နေစဉ်အတွင်း စက်ကိရိယာများနှင့် ဆားကစ်များ၏ ကပ်ပါးပါရာမီတာများမှ ထုတ်ပေးသော ဗို့အားမြင့် ပဲ့တင်ထပ်ခြင်း၊ နှင့် high voltage shocks များအတွင်း Ggd မှတဆင့် မြင့်မားသောဗို့အား သွယ်တန်းခြင်း (မိုးကြိုးပစ်စမ်းသပ်စဉ်တွင် ပိုအဖြစ်များသော အမှား)။

Gate Voltage ချို့ယွင်းချက်များကို ကာကွယ်ရန် အစီအမံများ

ဂိတ်နှင့်ရင်းမြစ်ကြား ဗို့အားကိုကာကွယ်ခြင်း- ဂိတ်နှင့်ရင်းမြစ်ကြားရှိ impedance မြင့်မားသောအခါ၊ ဂိတ်နှင့်ရင်းမြစ်ကြားရှိ ဗို့အားရုတ်တရက်ပြောင်းလဲမှုသည် လျှပ်ကူးပစ္စည်းများကြားရှိ capacitance မှတဆင့် gate သို့ တွဲဆက်ကာ UGS ဗို့အားလွန်ကဲမှုအား ဖြစ်ပေါ်စေသည်၊ ဂိတ်စည်းမျဥ်းများ လွန်ကဲလာစေသည်။ အမြဲတမ်း oxidative ပျက်စီးခြင်း။ UGS သည် အပြုသဘောဆောင်သော ယာယီဗို့အားတွင်ရှိနေပါက၊ စက်သည်လည်း အမှားအယွင်းများဖြစ်စေနိုင်သည်။ ဤအခြေခံအရ၊ gate drive circuit ၏ impedance ကို သင့်လျော်စွာ လျှော့ချသင့်ပြီး damping resistor သို့မဟုတ် 20V stabilizing voltage ကို gate နှင့် source ကြားတွင် ချိတ်ဆက်ထားသင့်သည်။ တံခါးဖွင့်ခြင်း မဖြစ်အောင် အထူးဂရုစိုက်သင့်သည်။

discharge tubes များကြား ဗို့အား လွန်ကဲခြင်းမှ ကာကွယ်ခြင်း- circuit တွင် inductor ရှိပါက၊ unit ကို ပိတ်လိုက်သောအခါ ယိုစိမ့်သော လျှပ်စီးကြောင်း (di/dt) တွင် ရုတ်တရက် ပြောင်းလဲမှု များသည် supply voltage ထက် ကောင်းမွန်စွာ ယိုစိမ့်မှု ဖြစ်ပေါ်ပြီး ယူနစ်ကို ပျက်စီးစေပါသည်။ ကာကွယ်မှုတွင် Zener Clamp၊ RC Clamp သို့မဟုတ် RC ဖိနှိပ်မှုပတ်လမ်း ပါဝင်သင့်သည်။