D-FET သည် 0 ဂိတ်ဘက်လိုက်မှု၌ ချန်နယ်တည်ရှိမှုအား FET ကို လုပ်ဆောင်နိုင်သည်; E-FET သည် 0 ဂိတ်ဘက်လိုက်မှု၌ ချန်နယ်မရှိသောအခါတွင် FET ကို ဆောင်ရွက်နိုင်မည်မဟုတ်ပေ။ ဤ FET အမျိုးအစားနှစ်မျိုးတွင် ၎င်းတို့၏ကိုယ်ပိုင်လက္ခဏာများနှင့် အသုံးပြုမှုများရှိသည်။ ယေဘုယျအားဖြင့်၊ မြန်နှုန်းမြင့်၊ ပါဝါနည်းပါးသော ဆားကစ်များတွင် မြှင့်တင်ထားသော FET သည် အလွန်တန်ဖိုးရှိသည်။ ဤစက်ပစ္စည်းသည် အလုပ်လုပ်နေသည်၊ ၎င်းသည် gate bias vo ၏ polarity ဖြစ်သည်။ltage နှင့်မြောင်း တူညီသော voltage သည် circuit design တွင်ပိုမိုအဆင်ပြေသည်။

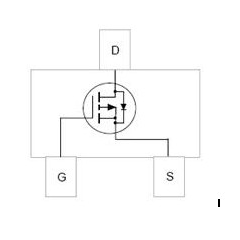

မြှင့်တင်ထားသော အဓိပ္ပါယ်မှာ- VGS = 0 tube သည် ဖြတ်တောက်ထားသော အခြေအနေတစ်ခုဖြစ်ပြီး မှန်ကန်သော VGS ဖြစ်သောအခါ၊ carriers အများစုသည် ဂိတ်ပေါက်ဆီသို့ ဆွဲဆောင်ခံရပြီး ဒေသတွင်းရှိ carriers များကို "မြှင့်တင်" ကာ conductive channel တစ်ခုအဖြစ် ဖန်တီးပေးပါသည်။ n-channel မြှင့်တင်ထားသော MOSFET သည် အခြေခံအားဖြင့် SiO2 ဖလင် insulation အလွှာ၏မျိုးဆက်ပေါ်ရှိ P-type semiconductor ဖြစ်သည့် ဘယ်ညာ symmetrical topology တစ်ခုဖြစ်သည်။ ၎င်းသည် P-type semiconductor တွင် SiO2 ဖလင်၏ insulating layer ကိုထုတ်ပေးပြီး လွန်စွာ doped N-type ဒေသနှစ်ခုကို ပျံ့နှံ့စေသည်။ဓါတ်ပုံရိုက်နည်းN-type ဒေသမှ လျှပ်ကူးပစ္စည်းများကို ပို့ဆောင်ပေးကာ၊ မြောင်း D အတွက် တစ်ခုနှင့် အရင်းအမြစ် S အတွက် တစ်ခု။ အလူမီနီယမ် သတ္တုအလွှာကို အရင်းအမြစ်နှင့် မြောင်းကြားရှိ လျှပ်ကာအလွှာပေါ်တွင် ချထားသည်။ G ဂိတ်ပေါက်အဖြစ် VGS = 0 V သောအခါ၊ D နှင့် S အကြားဗို့အား D နှင့် S အကြားတွင် back-to-back diodes ပါသော diodes အနည်းငယ်ရှိပါသည်။ D နှင့် S အကြား လျှပ်စီးကြောင်းသည် အသုံးပြုထားသော ဗို့အားဖြင့် ဖွဲ့စည်းထားခြင်းမဟုတ်ပါ။ .

ဂိတ်ဗို့အား ပေါင်းထည့်သောအခါ၊ 0 < VGS < VGS(th) ဆိုလျှင် တံခါးနှင့် အလွှာကြားရှိ capacitive လျှပ်စစ်စက်ကွင်းမှတဆင့်၊ ဂိတ်အောက်ခြေအနီးရှိ P-type ဆီမီးကွန်ဒတ်တာရှိ ပိုလီယွန်အပေါက်များကို အောက်ဘက်သို့ တွန်းထုတ်ပြီး၊ အနုတ်လက္ခဏာဆောင်သော အိုင်းယွန်းများ၏ ပါးလွှာသော အလွှာတစ်ခု ပေါ်လာသည်။ တစ်ချိန်တည်းမှာပင်၊ ၎င်းသည် မျက်နှာပြင်အလွှာသို့ ရွှေ့ရန် ယင်းရှိ oligons များကို ဆွဲဆောင်နိုင်သော်လည်း အရေအတွက်မှာ အကန့်အသတ်ရှိပြီး မြောင်းနှင့် ရင်းမြစ်ကို ဆက်သွယ်ပေးသည့် conductive channel တစ်ခုဖွဲ့စည်းရန် မလုံလောက်သောကြောင့် drain current ID ဖွဲ့စည်းခြင်းအတွက် မလုံလောက်သေးပါ။ နောက်ထပ်တိုး VGS တုန်းက VGS > VGS (th) (VGS (th) ကို turn-on voltage ဟုခေါ်သည်) အဘယ်ကြောင့်ဆိုသော် ယခုအချိန်တွင် gate voltage သည် အတော်အတန်အားကောင်းနေပြီဖြစ်သောကြောင့် P-type semiconductor မျက်နှာပြင်အလွှာတွင် gate ၏အောက်ခြေအောက်ခြေနားရှိ gate voltage သည် ပို၍စုဝေးနေပါသည်။ အီလက်ထရွန်၊ သင်သည် ကတုတ်ကျင်း၊ မြောင်းနှင့် ဆက်သွယ်ရေးအရင်းအမြစ်ကို ဖန်တီးနိုင်သည်။ အကယ်၍ Drain source ဗို့အား ပေါင်းထည့်ပါက Drain current ကို ID ဖြင့် ဖွဲ့စည်းနိုင်သည်။ P-type semiconductor polarity နှင့် carrier hole သည် တံခါးအောက်ရှိ conductive channel တွင် electrons ဆန့်ကျင်ဘက်ဖြစ်သောကြောင့် anti-type layer ဟုခေါ်သည်။ VGS ဆက်လက်တိုးလာသည်နှင့်အမျှ ID သည် ဆက်လက်တိုးလာပါမည်။ VGS = 0V တွင် ID = 0 ရှိပြီး၊ VGS > VGS(th) ပြီးနောက်တွင်သာ ယိုစီးမှုဖြစ်ပေါ်သောကြောင့် ဤ MOSFET အမျိုးအစားကို မြှင့်တင်မှု MOSFET ဟုခေါ်သည်။

စီးဆင်းနေသော လျှပ်စီးကြောင်းပေါ်ရှိ VGS ၏ ထိန်းချုပ်မှု ဆက်နွယ်မှုကို မျဉ်းကွေး iD = f(VGS(th))|VDS=const ဟုခေါ်သော လွှဲပြောင်းခြင်းဝိသေသမျဉ်းကွေးဟုခေါ်သော၊ နှင့် လွှဲပြောင်းဝိသေသမျဉ်းကွေး၏ လျှောစောက်ပမာဏ၊ gm၊ ဂိတ်ရင်းမြစ်ဗို့အားဖြင့် Drain current ထိန်းချုပ်မှုကို ထင်ဟပ်စေသည်။ gm ၏ ပြင်းအားသည် mA/V ဖြစ်သောကြောင့် gm ကို transconductance ဟုခေါ်သည်။